SmartMemories - The Stanford Smart Memories: A 90nm, 55M transistor, 61mm², 8-core chip multiprocessor

-

Upload

-

0

-

Embed

-

Share

-

Upload and view presentations on any device and embed the player to your website! --- > >Upload PPT

- Upload PPT

Download this Presentation

Presentation Transcript

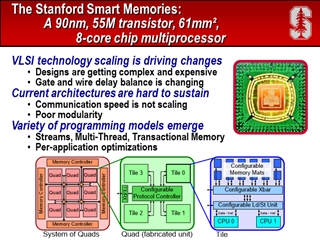

- 1.The Stanford Smart Memories: A 90nm, 55M transistor, 61mm², 8-core chip multiprocessor VLSI technology scaling is driving changes Designs are getting complex and expensive Gate and wire delay balance is changing Current architectures are hard to sustain Communication speed is not scaling Poor modularity Variety of programming models emerge Streams, Multi-Thread, Transactional Memory Per-application optimizations

- 2.Design Methodologies Use of Tensilica™ cores Hierarchical verification ProcTileQuad4-Quads Use of Relaxed Scoreboards for efficient system verification Design emulation using Bee2 Design & Physical Implementation Single Quad – 8 Processors in 4 Tiles + 1 Protocol Controller Physical Statistics & Floor Plan 55M transistors, 2.5M instances ST CMOS 90nm Multi-Vt Nominal Operation: 1.4W @181MHz 1.0V core, 1.8V IO 22-181MHz variable speed IO clock Fully fine-grained clock gated 7.8mm 7.8mm

- 3.Testing Platform SM a b c d Bring-up Test Platform SM test chip Custom ‘daughter’ board Control FPGA on Bee2 board Custom double-ended DIMM cards State Of The Testing System configuration .............. Proc’s running programs ........ So far so good… testing continues Related Publications Mai_isca’00, Mai_isscc’04, Labonte_pact’04, Leverich_isca’07, Solomatnikov_dac’07, Shacham_micro’08, Firoozshahian_isca’09 Test Chip Bee2 FPGA Board First Heartbeat

Related